## Contents HP E2259A Double-Wide Breadboard User's Manual Edition 2

| Warranty                                  | 3    |

|-------------------------------------------|------|

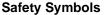

| Safety Symbols                            |      |

| WARNINGS                                  |      |

| Declaration of Conformity                 |      |

| Reader Comment Sheet                      |      |

|                                           |      |

| Chapter 1                                 |      |

| Getting Started                           | 9    |

| What's in this Manual?                    | 9    |

| Module Description                        | 9    |

| General Features                          | 9    |

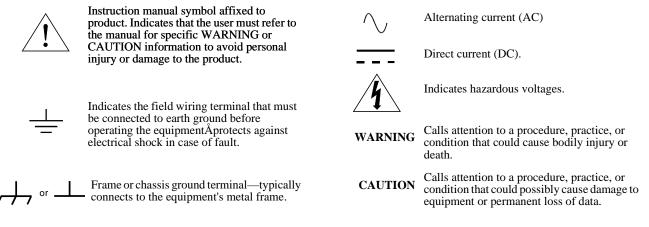

| Block Diagram Description                 | . 10 |

| Configuring the Module                    | . 12 |

| Connectors and Access Pads Description    | . 13 |

| J100, J101, J104, and J105 Pin Assignment |      |

| J102 and J103 Pin Assignment              | . 15 |

| P100, P101, and P102 Pin Assignment       | . 16 |

| Assembling the Field Wiring Connector     | . 18 |

|                                           |      |

| Chapter 2                                 |      |

| Using the Breadboard                      |      |

| What's in This Chapter                    |      |

| Registers                                 |      |

| Writing Data to Output Registers          |      |

| Using the Write Decoder Lines             |      |

| Reading Data From Input Registers         |      |

| Using the Read Decoder Lines              |      |

| Using the Interrupt                       |      |

| Program Example                           |      |

| Resetting the Module                      |      |

| Hardware Reset                            | . 28 |

| Software Reset                            | . 28 |

| Using the Power Supplies                  | . 28 |

| Application Example                       | . 29 |

| Relay Selection                           | 20   |

|                                           | . 29 |

| Chapter 3                                 | . 29 |

| Register Descriptions                         |  |

|-----------------------------------------------|--|

| About This Chapter                            |  |

| Register Addressing in the VXIbus Environment |  |

| Logical Address                               |  |

| A16/A24 Memory Mapping                        |  |

| Determining a Module's A16 Base Address       |  |

| Addressing A16 Registers                      |  |

| Addressing A24 Registers                      |  |

| Program Example                               |  |

| Register Descriptions                         |  |

| Registers in A16 Address Space                |  |

| Registers in A24 Address Space                |  |

| Appendix A               |       |

|--------------------------|-------|

| HP E2259A Specifications | <br>5 |

#### Certification

Hewlett-Packard Company certifies that this product met its published specifications at the time of shipment from the factory. Hewlett-Packard further certifies that its calibration measurements are traceable to the United States National Institute of Standards and Technology (formerly National Bureau of Standards), to the extent allowed by that organization's calibration facility, and to the calibration facilities of other International Standards Organization members.

#### Warranty

This Hewlett-Packard product is warranted against defects in materials and workmanship for a period of three years from date of shipment. Duration and conditions of warranty for this product may be superseded when the product is integrated into (becomes a part of) other HP products. During the warranty period, Hewlett-Packard Company will, at its option, either repair or replace products which prove to be defective.

For warranty service or repair, this product must be returned to a service facility designated by Hewlett-Packard (HP). Buyer shall prepay shipping charges to HP and HP shall pay shipping charges to return the product to Buyer. However, Buyer shall pay all shipping charges, duties, and taxes for products returned to HP from another country

HP warrants that its software and firmware designated by HP for use with a product will execute its programming instructions when properly installed on that product. HP does not warrant that the operation of the product, or software, or firmware will be uninterrupted or error free.

#### Limitation Of Warranty

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by Buyer, Buyer-supplied products or interfacing, unauthorized modification or misuse, operation outside of the environmental specifications for the product, or improper site preparation or maintenance.

The design and implementation of any circuit on this product is the sole responsibility of the Buyer. HP does not warrant the Buyer's circuitry or malfunctions of HP products that result from the Buyer's circuitry. In addition, HP does not warrant any damage that occurs as a result of the Buyer's circuit or any defects that result from Buyer-supplied products.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. HP SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### **Exclusive Remedies**

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. HP SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

#### Notice

The information contained in this document is subject to change without notice. HEWLETT-PACKARD (HP) MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. HP shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material. This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced, or translated to another language without the prior written consent of Hewlett-Packard Company. HP assumes no responsibility for the use or reliability of its software on equipment that is not furnished by HP.

#### **U.S. Government Restricted Rights**

The Software and Documentation have been developed entirely at private expense. They are delivered and licensed as "commercial computer software" as defined in DFARS 252.227-7013 (Oct 1988), DFARS 252.211-7015 (May 1991) or DFARS 252.227-7014 (Jun 1995), as a "commercial item" as defined in FAR 2.101(a), or as "Restricted computer software" as defined in FAR 52.227-19 (Jun 1987)(or any equivalent agency regulation or contract clause), whichever is applicable. You have only those rights provided for such Software and Documentation by the applicable FAR or DFARS clause or the HP standard software agreement for the product involved

HP E2259A Double-Wide Breadboard M-Module User's Manual and Programming Guide Edition 2 Copyright © 1998 Hewlett-Packard Company. All Rights Reserved.

#### **Documentation History**

All Editions and Updates of this manual and their creation date are listed below. The first Edition of the manual is Edition 1. The Edition number increments by 1 whenever the manual is revised. Updates, which are issued between Editions, contain replacement pages to correct or add additional information to the current Edition of the manual. Whenever a new Edition is created, it will contain all of the Update information for the previous Edition. Each new Edition or Update also includes a revised copy of this documentation history page.

| Edition 1 | <br> | <br>• • • • | <br> | <br> | <br>June 1997 |  |

|-----------|------|-------------|------|------|---------------|--|

| Edition 2 | <br> | <br>        | <br> | <br> | <br>May 1998  |  |

#### WARNINGS

The following general safety precautions must be observed during all phases of operation, service, and repair of this product. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the product. Hewlett-Packard Company assumes no liability for the customer's failure to comply with these requirements.

**Ground the equipment:** For Safety Class 1 equipment (equipment having a protective earth terminal), an uninterruptible safety earth ground must be provided from the mains power source to the product input wiring terminals or supplied power cable.

DO NOT operate the product in an explosive atmosphere or in the presence of flammable gases or fumes.

For continued protection against fire, replace the line fuse(s) only with fuse(s) of the same voltage and current rating and type. DO NOT use repaired fuses or short-circuited fuse holders.

**Keep away from live circuits:** Operating personnel must not remove equipment covers or shields. Procedures involving the removal of covers or shields are for use by service-trained personnel only. Under certain conditions, dangerous voltages may exist even with the equipment switched off. To avoid dangerous electrical shock, DO NOT perform procedures involving cover or shield removal unless you are qualified to do so.

**DO NOT operate damaged equipment:** Whenever it is possible that the safety protection features built into this product have been impaired, either through physical damage, excessive moisture, or any other reason, REMOVE POWER and do not use the product until safe operation can be verified by service-trained personnel. If necessary, return the product to a Hewlett-Packard Sales and Service Office for service and repair to ensure that safety features are maintained.

**DO NOT service or adjust alone:** Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

**DO NOT substitute parts or modify equipment:** Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification to the product. Return the product to a Hewlett-Packard Sales and Service Office for service and repair to ensure that safety features are maintained.

|                                            | Declaration of Conformity                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| according to ISO/IEC Guide 22 and EN 45014 |                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Manufacturer's Na                          | me: Hewlett-Packard Company<br>Loveland Manufacturing Center                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Manufacturer's Ac                          | ldress: 815 14th Street S.W.<br>Loveland, Colorado 80537                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| declares, that the pro-                    | oduct:                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Product Name:                              | Double-Wide Breadboard M-Module                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Model Number:                              | HP E2259A                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Product Options:                           | All                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Safety:                                    | Diving Product Specifications:<br>IEC 1010-1 (1990) Incl. Amend 2 (1996)/EN61010-1 (1993)<br>CSA C22.2 #1010.1 (1992)<br>UL 3111-1 (1994)                                                                                                                                                                                                                                                                                   |  |  |  |

| EMC:                                       | CISPR 11:1990/EN55011 (1991): Group1 Class A<br>EN61000-3-2:1995 Class A<br>EN50082-1:1992<br>IEC 801-2:1991: 4kV CD, 8kV AD<br>IEC 801-3:1984: 3 V/m<br>IEC 801-4:1988: 1kV Power Line, 0.5kV Signal Lines<br>ENV50141:1993/prEN50082-1 (1995): 3 Vrms<br>ENV50142:1994/prEN50082-1 (1995): 1 kV CM, 0.5 kV DM<br>IEC1000-4-8:1993/prEN50082-1 (1995): 3 A/m<br>EN61000-4-11:1994/prEN50082-1 (1995): 30%, 10ms 60%, 100ms |  |  |  |

|                                            | ormation: The product herewith complies with the requirements of the Low Voltage Direct EMC Directive 89/336/EEC (inclusive 93/68/EEC) and carries the "CE" mark accordingly                                                                                                                                                                                                                                                |  |  |  |

| Tested in a typical c                      | onfiguration in an HP C-Size VXI mainframe.                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

Im White

Jim White, Quality Manager

European contact: Your local Hewlett-Packard Sales and Service Office or Hewlett-Packard GmbH, Department HQ-TRE, Herrenberger Straße 130, D-71034 Böblingen, Germany (FAX: +49-7031-14-3143)

April 7, 1997

#### **Reader Comment Sheet**

HP E2259A Double-Wide Breadboard M-Module User's Manual and Programming Guide Edition 2

| Your Name                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                 | City, St                                                                                                                                                  | ate/Provinc                               | e                                                    |                             |                                     |                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------|-----------------------------|-------------------------------------|-----------------------------|

| Company Name                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                 | Country                                                                                                                                                   | /                                         |                                                      |                             |                                     |                             |

| Job Title                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                 | Zip/Pos                                                                                                                                                   | tal Code                                  |                                                      |                             |                                     |                             |

| Address                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                 | Telepho                                                                                                                                                   | one Numbe                                 | r with Area                                          | a Code                      |                                     |                             |

| lease list the system con                                                                                                                                                                 | ntroller, operating system, progra                                                                                                                                                                                                                                                                                                              | amming language,                                                                                                                                          | and plug                                  | -in modu                                             | les you a                   | re using.                           |                             |

|                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                 | fold here                                                                                                                                                 |                                           |                                                      |                             |                                     |                             |

|                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                           |                                           |                                                      |                             | NEC                                 | POSTAGE<br>ESSARY<br>MAILED |

|                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                           |                                           |                                                      |                             |                                     | N THE                       |

|                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                           |                                           | A 11                                                 | ٦                           | •••••                               |                             |

|                                                                                                                                                                                           | BUSINESS                                                                                                                                                                                                                                                                                                                                        | K K F PI                                                                                                                                                  | Y IVI                                     |                                                      | _                           |                                     |                             |

|                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                           |                                           |                                                      |                             |                                     |                             |

|                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                 | MIT NO. 37 LOV                                                                                                                                            | /ELAND,                                   |                                                      |                             |                                     |                             |

|                                                                                                                                                                                           | FIRST CLASS PERM                                                                                                                                                                                                                                                                                                                                | MIT NO. 37 LOV<br>ADDRESSEE                                                                                                                               | /ELAND,                                   |                                                      |                             |                                     |                             |

|                                                                                                                                                                                           | FIRST CLASS PERM<br>POSTAGE WILL BE PAID BY                                                                                                                                                                                                                                                                                                     | MIT NO. 37 LOV<br>ADDRESSEE<br>RD COMPAN<br>Division<br>Intment                                                                                           | /ELAND,                                   |                                                      |                             |                                     |                             |

|                                                                                                                                                                                           | FIRST CLASS PERM<br>POSTAGE WILL BE PAID BY<br>HEWLETT-PACKAR<br>Measurement Systems I<br>Learning Products Depa<br>P.O. Box 301                                                                                                                                                                                                                | MIT NO. 37 LOV<br>ADDRESSEE<br>RD COMPAN<br>Division<br>urtment                                                                                           | /ELAND,                                   | CO                                                   | J                           |                                     |                             |

|                                                                                                                                                                                           | FIRST CLASS PERM<br>POSTAGE WILL BE PAID BY<br><b>HEWLETT-PACKAR</b><br>Measurement Systems I<br>Learning Products Depa<br>P.O. Box 301<br>Loveland, CO 80539-99                                                                                                                                                                                | MIT NO. 37 LOV<br>ADDRESSEE<br>RD COMPAN<br>Division<br>urtment<br>984                                                                                    | /ELAND,<br><b>Y</b>                       | CO                                                   |                             |                                     |                             |

| _                                                                                                                                                                                         | FIRST CLASS PERM<br>POSTAGE WILL BE PAID BY<br><b>HEWLETT-PACKAR</b><br>Measurement Systems I<br>Learning Products Depa<br>P.O. Box 301<br>Loveland, CO 80539-99                                                                                                                                                                                | MIT NO. 37 LOV<br>ADDRESSEE<br><b>RD COMPAN</b><br>Division<br>urtment<br>984<br>IIIIIII<br>6014 here<br>Disagree                                         | /ELAND,<br>Y<br>                          | <u>co</u><br>Iılılıılıl                              | <b>_</b> _                  | ► Agree                             |                             |

| <ul><li>The documentation</li><li>Instructions are ea</li></ul>                                                                                                                           | FIRST CLASS PERM<br>POSTAGE WILL BE PAID BY<br><b>HEWLETT-PACKAR</b><br>Measurement Systems I<br>Learning Products Depa<br>P.O. Box 301<br>Loveland, CO 80539-99                                                                                                                                                                                | MIT NO. 37 LOV<br>ADDRESSEE<br><b>RD COMPAN</b><br>Division<br>Uritment<br>984<br>IIIIIII<br>601d here<br>Disagree<br>O<br>O                              | Y<br>Y<br>0<br>0                          | <u>co</u><br>Iılılıılıl<br>                          | <br>                        | ► Agree<br>O<br>O                   |                             |

| <ul> <li>The documentation</li> <li>Instructions are ea</li> <li>The documentation</li> <li>Examples are clear</li> </ul>                                                                 | FIRST CLASS PERM<br>POSTAGE WILL BE PAID BY<br><b>HEWLETT-PACKAR</b><br>Measurement Systems I<br>Learning Products Depa<br>P.O. Box 301<br>Loveland, CO 80539-99<br>le for each statement below:<br>n is well organized.<br>sy to understand.<br>n is clearly written.<br>r and useful.                                                         | MIT NO. 37 LOV<br>ADDRESSEE<br><b>RD COMPAN</b><br>Division<br>Uritment<br>984<br>IIIIIII<br>984                                                          | Y<br>Y<br>0<br>0<br>0<br>0<br>0           | <u>co</u><br>          <br>                          |                             | ► Agree<br>O<br>O<br>O<br>O         |                             |

| <ul> <li>The documentation</li> <li>Instructions are ea</li> <li>The documentation</li> <li>Examples are clear</li> <li>Illustrations are cleared</li> </ul>                              | FIRST CLASS PERM<br>POSTAGE WILL BE PAID BY<br><b>HEWLETT-PACKAR</b><br>Measurement Systems I<br>Learning Products Depa<br>P.O. Box 301<br>Loveland, CO 80539-99<br>le for each statement below:<br>n is well organized.<br>sy to understand.<br>n is clearly written.<br>r and useful.                                                         | MIT NO. 37 LOV<br>ADDRESSEE<br>AD COMPAN<br>Division<br>Intment<br>984<br>IIIIIIII<br>60Id here<br>Disagree<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O       | Y<br>Y<br>0<br>0<br>0<br>0                | <u>co</u><br>Iılılıılıl<br>                          | ulululul<br><br>0<br>0<br>0 | ► Agree<br>O<br>O<br>O              |                             |

| <ul> <li>The documentation</li> <li>Instructions are ea</li> <li>The documentation</li> <li>Examples are clear</li> <li>Illustrations are clear</li> <li>The documentation</li> </ul>     | FIRST CLASS PERM<br>POSTAGE WILL BE PAID BY<br><b>HEWLETT-PACKAR</b><br>Measurement Systems I<br>Learning Products Depa<br>P.O. Box 301<br>Loveland, CO 80539-99<br>le for each statement below:<br>n is well organized.<br>sy to understand.<br>n is clearly written.<br>r and useful.<br>ear and helpful.<br>n meets my overall expectations. | MIT NO. 37 LOV<br>ADDRESSEE<br><b>RD COMPAN</b><br>Division<br>Intrent<br>984<br>IIIIIII<br>601d here<br>Disagree<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | Y<br>Y<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | <u>co</u><br>Iılılıılıl<br><br>0<br>0<br>0<br>0<br>0 |                             | Agree<br>O<br>O<br>O<br>O<br>O<br>O |                             |

| <ul> <li>The documentation</li> <li>Instructions are ea</li> <li>The documentation</li> <li>Examples are cleated</li> <li>Illustrations are cleated</li> <li>The documentation</li> </ul> | FIRST CLASS PERM<br>POSTAGE WILL BE PAID BY<br><b>HEWLETT-PACKAR</b><br>Measurement Systems I<br>Learning Products Depa<br>P.O. Box 301<br>Loveland, CO 80539-99<br>le for each statement below:<br>n is well organized.<br>sy to understand.<br>n is clearly written.<br>r and useful.<br>ear and helpful.                                     | MIT NO. 37 LOV<br>ADDRESSEE<br><b>RD COMPAN</b><br>Division<br>Intrent<br>984<br>IIIIIII<br>601d here<br>Disagree<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | Y<br>Y<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | <u>co</u><br>Iılılıılıl<br><br>0<br>0<br>0<br>0<br>0 |                             | Agree<br>O<br>O<br>O<br>O<br>O<br>O |                             |

| <ul> <li>The documentation</li> <li>Instructions are ea</li> <li>The documentation</li> <li>Examples are cleated</li> <li>Illustrations are cleated</li> <li>The documentation</li> </ul> | FIRST CLASS PERM<br>POSTAGE WILL BE PAID BY<br><b>HEWLETT-PACKAR</b><br>Measurement Systems I<br>Learning Products Depa<br>P.O. Box 301<br>Loveland, CO 80539-99<br>le for each statement below:<br>n is well organized.<br>sy to understand.<br>n is clearly written.<br>r and useful.<br>ear and helpful.<br>n meets my overall expectations. | MIT NO. 37 LOV<br>ADDRESSEE<br><b>RD COMPAN</b><br>Division<br>Intrent<br>984<br>IIIIIII<br>601d here<br>Disagree<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | Y<br>Y<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | <u>co</u><br>Iılılıılıl<br><br>0<br>0<br>0<br>0<br>0 |                             | Agree<br>O<br>O<br>O<br>O<br>O<br>O |                             |

## What's in this Manual?

This manual contains a module description, configuration and wiring information, and general programming information for the HP E2259A Double-Wide Breadboard M-Module. Complete specifications for the breadboard are provided in Appendix A.

The HP E2259A is intended to be installed on a carrier such as the HP E2251 M-Module Carrier. Refer to the Carrier documentation for M-Module installation information.

This chapter contains general features, a block diagram description, configuration information and connector pinouts for the HP E2259A.

# **Module Description**

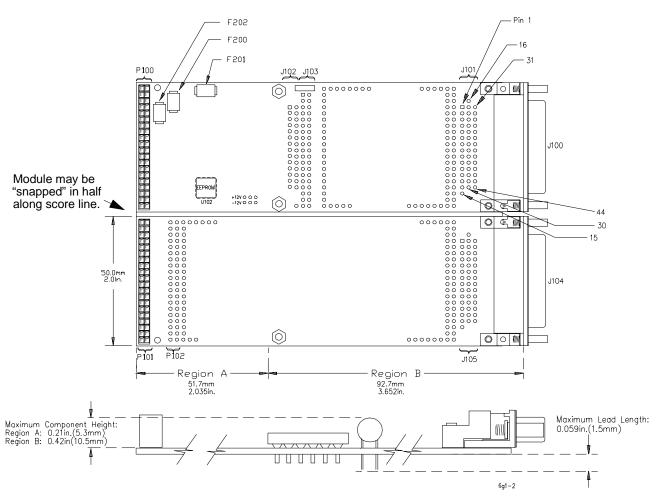

The HP E2259A is a double-wide breadboard M-Module. As a double-wide module it occupies two adjacent slots in the Carrier. However, it is scored down the middle and can easily be "snapped" in half; with all the active M-Module interface circuits on one of the two halves. See Figure 1-2.

Even though the HP E2259A breadboard is a double-wide, in an HP E2251 Carrier, the module requires only one VXIbus logical address. When installed in the Carrier the module functions as a standard VXIbus device.

## General Features The HP E2259A provides:

- A8/D16 Register-based M-Module interface circuitry.

- A programmable BUSY Timer (for delaying interrupt acknowledgment of command completion).

- A 16-bit input/output (I/O) Register.

- Read/Write decoder lines

- Support for internal/external interrupts.

| Block Diagram<br>Description | Figure 1-1 shows a simplified block diagram of the HP E2259A. In order to effectively program the module you must understand its operation at a block diagram level. The following paragraphs describe the major sections in the block diagram.                                                                                                                                                                                                    |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Module Control               | This block contains all of the logic for the module including carrier interface, registers, interrupt control, the programmable busy timer, I/O lines, control lines, etc. All lines except the latched data output lines (BC0 - BC15) connect directly to the U101 controller FPGA.                                                                                                                                                               |

|                              | The I/O register at 14H in A24 memory space is realized on this Breadboard.<br>Writing to this register automatically outputs the data on the BC0 - BC15<br>lines; similarly, reading this register automatically reads the data on the TR0<br>- TR15 lines. More I/O registers can be expanded by using the decoder lines<br>and additional circuits.                                                                                             |

| ID EEPROM                    | The ID EEPROM holds sixty-four 16-bit words of M-Module ID data and VXI M-Module data.                                                                                                                                                                                                                                                                                                                                                             |

| Input and Output Circuit     | The breadboard data input lines (TR0 - TR15) connect directly from the J103 pads to the U101 controller FPGA. The data output lines (BC0 - BC15) are latched by U107 and U108 (74ACTQ273SM) and are available on J103. Control lines (LAT*, DBEN*, CRST*, etc.) and the I/O Decoder lines (WP0 - WP7 for write decoder lines and RP0 - RP7 for read decoder lines) are available on J102. Refer to Chapter 2 for information on using these lines. |

| Power Supplies               | The HP E2259A Breadboard provides filtered $\pm 12$ VDC and $\pm 5$ VDC supplies for use on the breadboard. Do not exceed the maximum current specifications for the breadboard (see Appendix A). The active electronics provided on the module use only the $\pm 5$ VDC supply.                                                                                                                                                                   |

|                              | Each power supply is protected by a positive-temperature-coefficient thermistor. When maximum current through the thermistor is reached, its resistance increases significantly thereby limiting the current; the thermistor acts like a resettable fuse. Table 1-1 lists the power supplies, thermistor protection reference designator (silkscreened on PC board), and the maximum current.                                                      |

+5VDC Supply

+12VDC Supply

-12VDC Supply

| Table 1-1. H | P E2259A Power Supply         | y Protection    |

|--------------|-------------------------------|-----------------|

|              | Thermistor Ref.<br>Designator | Maximum Current |

F201

F200

F202

| Thermistor Ref. | Maximum Current |

|-----------------|-----------------|

| Designator      |                 |

1000mA

200mA

200mA

Figure 1-1. HP E2259A Block Diagram

# **Configuring the Module**

This section provides general information to connect user wiring to the breadboard module and provides guidelines for mounting components on the module.

**Note** This section does not describe installing the breadboard module in a carrier. Since installation is dependent on the carrier used, you should refer to your carrier's documentation for detailed installation instructions. Each HP M-Module is supplied with identifying labels that should be installed on the carrier.

WARNING SHOCK HAZARD. Only qualified, service-trained personnel aware of the hazards involved should install, configure, or remove the M-Module. Disconnect all power sources from the mainframe, the terminal module and installed modules before installing or removing a module.

Caution VOLTAGE/CURRENT. Pay careful attention to the limitation of maximum voltage/current and maximum power listed in Appendix A. Exceeding any limit or use outside the parameters specified may damage the module and/or carrier.

Caution STATIC ELECTRICITY. Static electricity is a major cause of component failure. To prevent damage to the electrical components on an M-Module or the carrier, observe anti-static techniques whenever installing, removing, or working on a carrier or M-Module.

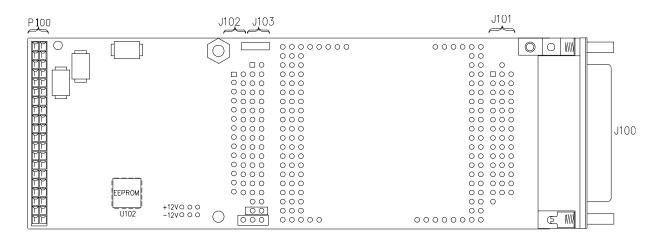

## **Connectors and Access Pads Description**

There are several connectors and access pads on the HP E2259A Breadboard. Refer to Figure 1-2. Connector P100 provides the carrier interface to the active electronics on the module. Connector P101 provides access to the carrier interface; all pins on P101 are mapped to access pads on P102 (refer to P100, P101, and P102 Pin Assignment on page 16 for detailed pinout). Access pads J102 and J103 provide access to the buffered input and output lines, read and write decoder lines, busy line, and power supply connections (refer to J102 and J103 Pin Assignment on page 15 for detailed pinout). Connectors J100 and J104 provide connections for user field wiring. J100 directly maps pin-for-pin to access pads on J101; J104 maps pin-for-pin to access pads on J105. Figure 1-2 also shows the maximum component height above the board and maximum lead length below the board.

Figure 1-2. HP E2259A Connectors Layout

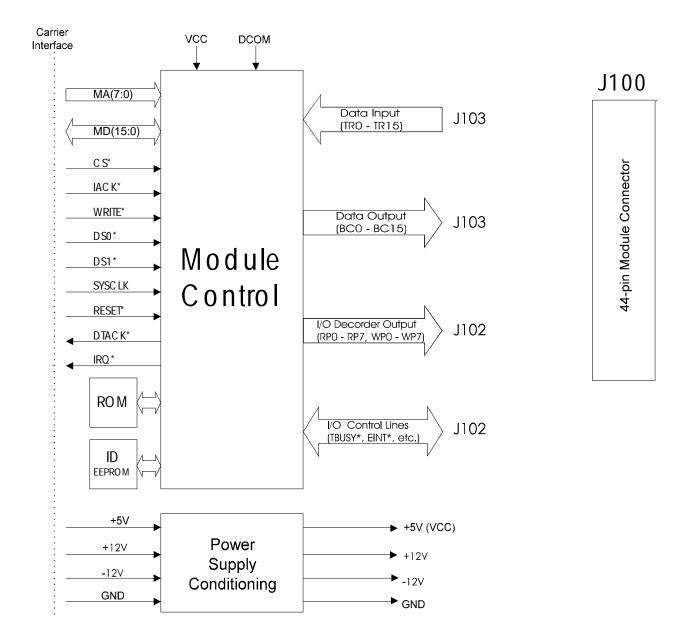

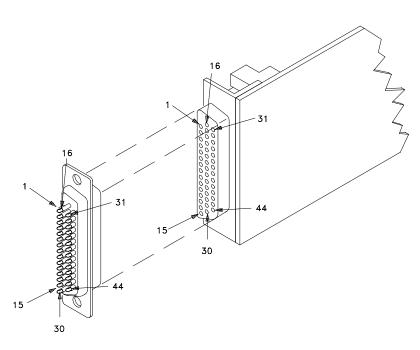

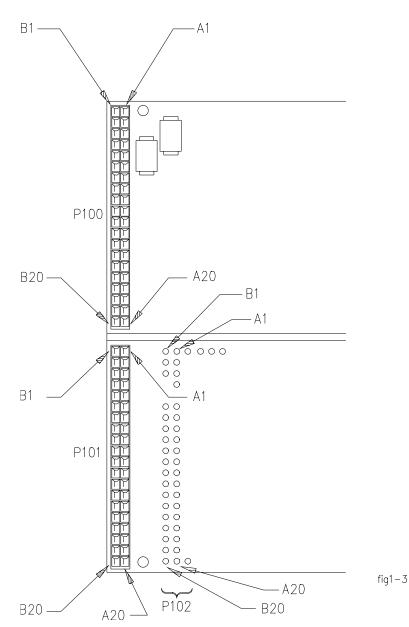

# J100, J101,J104, and J105 are for user field wiring.J100 maps pin-for-pinJ104, and J105J101,J104, and J105 are for user field wiring.J100 maps pin-for-pinJ104, and J105J101 (see Figure 1-2) and J104 maps pin-for-pin maps to J105.Figure 1-3Shows the 44-pin field wiring connector pinout.Figure 1-6 shows how toassemble the field wiring connector and hood assembly.

Figure 1-3. 44-Pin Field Wiring Connector

#### J102 and J103 Pin Assignment

Figure 1-4 shows the pinout for the J102 and J103 pads. Notice that the bottom row of pads on J103 (CGND) are connected to chassis ground through the carrier to the VXIbus mainframe. The  $\pm$ 12VDC pads are located just to the left of the bottom of J102.

|                                                                                            | J102                                                           |                                                                            |

|--------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------|

| RP7<br>RP5<br>RP1<br>WP7<br>WP5<br>WP3<br>WP1<br>BUSY*<br>CINT*<br>EINT*<br>CRST*<br>DBEN* | $ \begin{array}{c}             0 \\             0 \\         $ | RP6<br>RP2<br>RP0<br>WP6<br>WP4<br>WP0<br>+5V<br>+5V<br>+5V<br>GND<br>W14* |

| LAT*<br>EINT*<br>CRST*                                                                     |                                                                | +5V<br>GND<br>GND                                                          |

|        | J1 | 03 |      |

|--------|----|----|------|

| ŕ      | _  |    |      |

| TR0    |    | 0  | TR1  |

| TR2    | Ο  | 0  | TR3  |

| TR4    | -  | 0  | TR5  |

| TR6    | 0  | 0  | TR7  |

| TR8    | Ο  | 0  | TR9  |

| TR10   | 0  | -  | TR11 |

| TR12   | 0  | -  | TR13 |

| TR14   | 0  | -  | TR15 |

| BC0    | -  | 0  | BC1  |

| BC2    | 0  | ~  | BC3  |

| BC4    |    | 0  | BC5  |

| BC6    | 0  | -  | BC7  |

| BC8    | 0  | 0  | BC9  |

| BC10   | -  | 0  | BC11 |

| BC12   | 0  |    | BC13 |

| BC14   | 0  | 0  | BC15 |

| GND    | 0  | ~  | GND  |

| CGND O | 0  | 0  | CGND |

Figure 1-4. J102, J103 Connector Pinouts

**TR0 - TR15**: Data Input Lines (register address 14<sub>h</sub> in A24 Memory).

BC0 - BC15: Data Output Lines (register address 14<sub>h</sub> in A24 Memory).

- **WP0 WP7**: Write Decoder Lines (address  $20_h$ - $2E_h$  in A24 Memory).

- **RP0 RP7**: Read Decoder Lines (address 20<sub>h</sub>-2E<sub>h</sub> in A24 Memory).

- **BUSY\***: Delay Timer Output. (Delay Time Reg. Addr. 12<sub>h</sub> in A24) output from breadboard.

- **CINT\***: Clear Interrupt. A negative pulse is asserted during interrupt acknowledge if external interrupt request is pending, output from breadboard.

- **EINT\***: User Supplied External Interrupt Request. Falling edge causes interrupt to host controller if enabled.

LAT\*: Latch signal for write cycle, output from breadboard.

**CRST**\*: Reset, low means breadboard being reset, output from breadboard. **DBEN**\*: Data Bus Enable, low to enable data bus, output from breadboard.

W14\*: Output Register Latch Signal of 14H in A24 memory space, rising

edge latches data into external device, output from breadboard.

CGND: Chassis Ground

P100, P101, and P102 Pin Assignment

Figure 1-5 shows the connector pinouts for P100, P101, and P102. Pin 101 connects to and maps pin-for-pin to P102. The pin names are described on the next page.

| Pin | Col A      | Col B  |

|-----|------------|--------|

| 1   | CS*        | Ground |

| 2   | MA01       | +5V    |

| 3   | MA02       | +12V   |

| 4   | MA03       | -12V   |

| 5   | MA04       | Ground |

| 6   | MA05       | DREQ*  |

| 7   | MA06       | DACK*  |

| 8   | MA07       | Ground |

| 9   | MD08       | MD00   |

| 10  | MD09       | MD01   |

| 11  | MD10       | MD02   |

| 12  | MD11       | MD03   |

| 13  | MD12       | MD04   |

| 14  | MD13       | MD05   |

| 15  | MD14       | MD06   |

| 16  | MD15       | MD07   |

| 17  | DS1*       | DS0*   |

| 18  | DTACK<br>* | WRITE* |

| 19  | IACK*      | IRQ*   |

| 20  | RESET*     | SYSCLK |

#### Figure 1-5. P100, P101, P102 Connectors

| MA01 to MA07:        | M-Module Address Bus, Input to M-Module.                                        |

|----------------------|---------------------------------------------------------------------------------|

| CS*:                 | Card Select Signal, Input to M-Module. Low when the M-Module is being accessed. |

| <b>MD00 to MD15:</b> | M-Module Data Bus, Input / Output.                                              |

| DACK*:               | Low when carrier is performing a DMA transfer, Input                            |

|                      |                                                                                 |

|              | to M-Module.                                                                                                                                     |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| DREQ*:       | Low to requests a DMA transfer, Output from M-Module.                                                                                            |

| DS0* - DS1*: | Data Strobe Signal, Input to M-Module<br>00 = 16 bit data transfer<br>01 = D15 - D08 transfer<br>10 = D7 - D0 transfer<br>11 = no data transfer. |

| DTACK*:      | Data Acknowledge Signal, Output from M-Module.<br>Low to acknowledge data transfer and terminate access.                                         |

| IACK*:       | Interrupt Acknowledge Signal, Input to M-Module.<br>Low when interrupt is being acknowledged.                                                    |

| IRQ*:        | Interrupt Request Signal, Output from M-Module. Low to request an interrupt.                                                                     |

| RESET*:      | System Reset Signal, Input to M-Module. Low to reset the module.                                                                                 |

| SYSCLK:      | 16MHz System Clock, Input to M-Module.                                                                                                           |

| WRITE*:      | Write Signal, Input to M-Module. Low during writing cycle, high during reading cycle.                                                            |

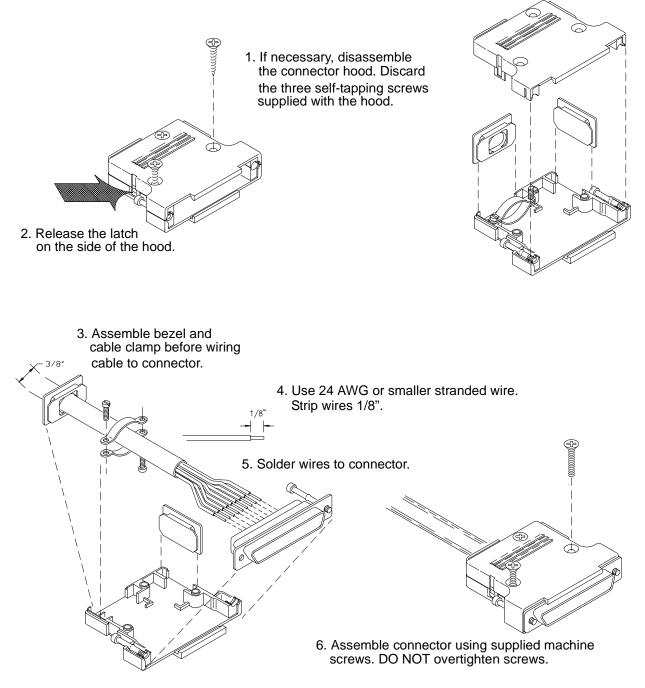

# **Assembling the Field Wiring Connector**

Each HP E2259A module includes two 44-pin connector and hood kits (HP kit part number E2273-01203). You must supply your own cable. The drawing below shows how to connect wiring and assemble the connector and hood.

Figure 1-6. Assembling the Field Wiring Connector and Hood

## What's in This Chapter

This chapter provides general operating information for the HP E2259A Double-wide Breadboard. It also provides a simple application example. The chapter contents include:

| • Writing Data to Output Registers  | Page 20 |

|-------------------------------------|---------|

| • Reading Data from Input Registers | Page 22 |

| • Using the Interrupt               | Page 24 |

| • Resetting the Module              | Page 28 |

| • Using the Power Supplies          | Page 28 |

| • Application Example               | Page 29 |

**Registers** Table 2-1 lists the registers available on the HP E2259A Breadboard (Chapter 3 provides a detailed description of all of the registers on the HP E2259A.) This section provides information on using the Input/Output Register and the Read/Write Decoder Registers.

| Register Name                | Register Address                  | Register Description                                                  |

|------------------------------|-----------------------------------|-----------------------------------------------------------------------|

| VXI ID Register              | 00 $_{ m h}$ in VXI A16 Memory    | Provides Device Class and Manufacturer ID.                            |

| VXI Device Type Register     | 02 $_{ m h}$ in VXI A16 Memory    | Provides Model Code for M-Module.                                     |

| VXI Status/Control Register  | 04 $_{ m h}$ in VXI A16 Memory    | Controls Reset and Provides module Status information.                |

| A24 Offset Register          | 06 $_{ m h}$ in VXI A16 Memory    | Provides A24 Offset Base Address.                                     |

| Interrupt Selection Register | 20 $_{ m h}$ in VXI A16 Memory    | Selects VXI Interrupt Line.                                           |

| Status Register              | 00 $_{ m h}$ in VXI A24 Memory    | Selects Interrupt Source.                                             |

| Control Register             | 02 $_{ m h}$ in VXI A24 Memory    | Controls Reset and Enables/Disables Interrupt.                        |

| Interrupt Register           | 04 $_{ m h}$ in VXI A24 Memory    | Selects Type of Interrupt.                                            |

| Delay Timer (BUSY) Register  | 12 $_{ m h}$ in VXI A24 Memory    | Sets Delay Value for Command completion interrupt.                    |

| Input/Output Register        | 14 $_{ m h}$ in VXI A24 Memory    | Data Input from TR0 - TR15 Lines.<br>Data Output to BC0 - BC15 Lines. |

| Read/Write Decoder Registers | $20_h$ - $2E_h$ in VXI A24 Memory | Used to select the latches or buffers supplied by users.              |

#### Table 2-1. HP E2259A Registers

# Writing Data to Output Registers

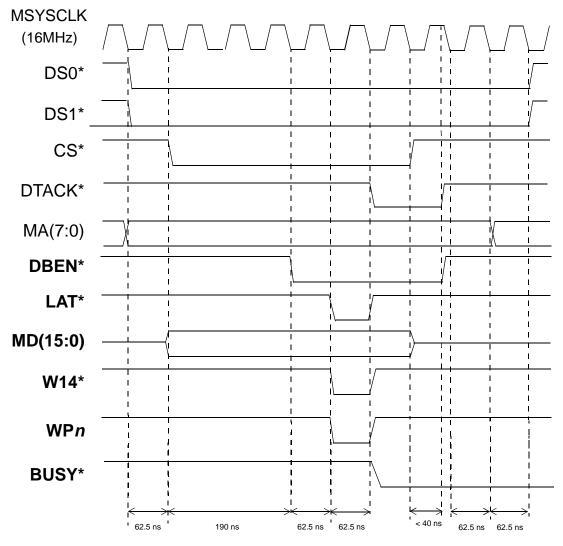

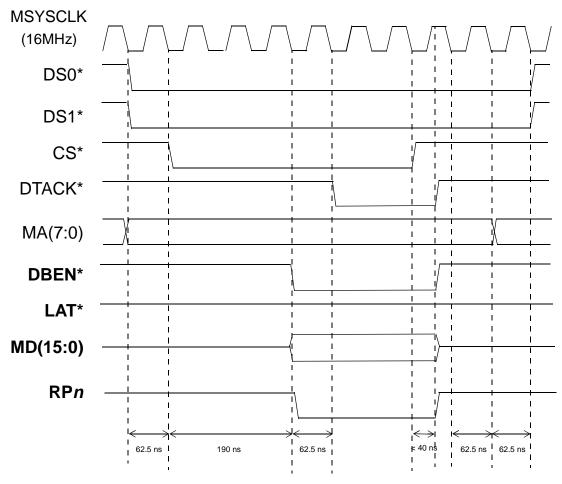

To output data over the data bus lines (BC0 - BC15), write the data to the I/O register at  $14_h$  in A24 Memory. Figure 2-1 shows the timing of writing data to the I/O register. You only have access to the DBEN\*, LAT\*, W14\*, and BUSY\* control lines; the other control line waveforms (SYSCLK, DS0\*, DS1\*, CS\*, DTACK\*, and MA0-MA7) are provided for reference information only. Note:

- W14\* has the same timing as LAT\* when writing to 14H in A24 memory space.

- IRQ\* is asserted at the end of the BUSY cycle (see "Using the Interrupt" on page 24). The BUSY\* line pulse lasts 13mS if the module default is used. You can change the BUSY time by writing a value to the Delay Timer Register at address 12<sub>h</sub>. Refer to Chapter 3 for details.

- MD15-MD0 are latched to BC15-BC0 at the rising edge of W14\*.

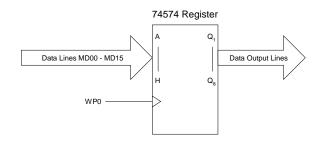

## Using the Write Decoder Lines

You can use the eight Write Decoder lines (WP0 - WP7) as latch select lines to expand for more output registers. Table 2-2 lists the Read/Write Decoder Register Addresses and the corresponding WP and RP lines.

| WP / RP Line | Register Address           | WP / RP Line | Register Address              |

|--------------|----------------------------|--------------|-------------------------------|

| WP0/ RP0     | $20_{ m h}$ in A24 Memory  | WP4 / RP4    | 28 <sub>h</sub> in A24 Memory |

| WP1 / RP1    | 22 $_{ m h}$ in A24 Memory | WP5 / RP5    | $2A_h$ in A24 Memory          |

| WP2 / RP2    | 24 $_{ m h}$ in A24 Memory | WP6 / RP6    | $2C_h$ in A24 Memory          |

| WP3 / RP3    | 26 $_{ m h}$ in A24 Memory | WP7 / RP7    | $2E_h$ in A24 Memory          |

Table 2-2. Read/Write Decoder Lines and Register Addresses

Figure 2-1 shows the timing required to write output data using one of the Read/Write Decoder Registers and the corresponding WP Line. You only have access to the DBEN\*, LAT\*, WP*n*, and BUSY control lines; the other control line waveforms (SYSCLK, DS0\*, etc.) are provided for reference information only.

- WP*n* has the same timing as LAT\* when writing to the corresponding register address.

- There is no BUSY signal when writing to addresses other than14H in A24 memory space.

- MD15-MD0 are latched to latches on the rising edge of WPn.

Figure 2-2 shows an example of using the WP0 Decoder Line to serve as a device latch signal.

To create an expanded register, write a data value to the appropriate Read/Write Decoder Register. For example, to use the circuit in Figure 2-2, you would write a 16-bit data value to the WP0 register (address  $20_h$  in A24 memory).

# **Reading Data From Input Registers**

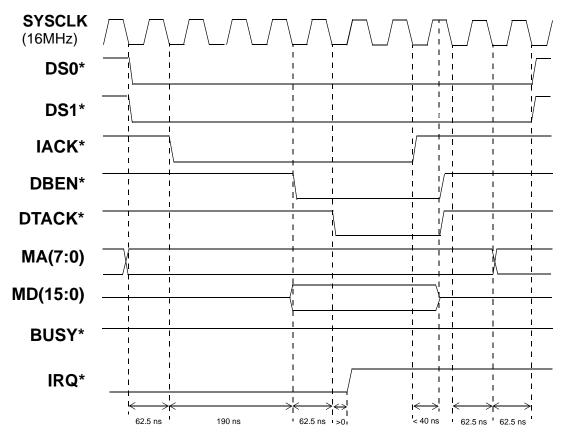

To read data from the TR0 - TR15 Data Input lines, read the data from the I/O register at  $14_h$  in A24 memory space. Figure 2-3 illustrates the timing required for reading data from this register on the HP E2259A Breadboard. You only have access to the DBEN\* and LAT\* control lines; the other control line waveforms are provided for reference information only.

Figure 2-3. Timing of Reading Data from Registers

## Using the Read Decoder Lines

Expanding input registers with read decoder lines RP0-RP7 is similar to expanding output registers (see Figure 2-2 on Page 21), except that a buffer (74245) is used as an input buffer, RPn is used as a buffer enable signal, data direction is toward MD15-MD0. The RPn lines can be used as select lines to specify which device the data is read from. Figure 2-3 also shows the timing of the RPn pulse. Table 2-3 lists the Read/Write Decoder Register Addresses and the corresponding WP and RP lines.

| WP / RP Line | Register Address           | WP / RP Line | Register Address           |

|--------------|----------------------------|--------------|----------------------------|

| WP0/ RP0     | 20 $_{ m h}$ in A24 Memory | WP4 / RP4    | 28 $_{ m h}$ in A24 Memory |

| WP1 / RP1    | 22 $_{ m h}$ in A24 Memory | WP5 / RP5    | $2A_h$ in A24 Memory       |

| WP2 / RP2    | 24 $_{ m h}$ in A24 Memory | WP6 / RP6    | $2C_h$ in A24 Memory       |

| WP3 / RP3    | $26_{ m h}$ in A24 Memory  | WP7 / RP7    | $2E_{h}$ in A24 Memory     |

Table 2-3. Read/Write Decoder Lines and Register Addresses

# **Using the Interrupt**

The Breadboard has a read only Interrupt Register located at address  $04_h$  in A24 Memory. The contents of this register is used as an interrupt vector to determine which interrupt source caused the interrupt.

If IACK\* (Type C interrupt) is present, the content of the Interrupt Register will be sent to the data bus and the IRQ\* line will be released. Reading the Interrupt Register will clear the interrupt request signal IRQ\* to support Type A interrupt.

Bits 2 through bit 15 of this register are not used. Bit 1 indicates an external interrupt existing if the content of bit 1 is "1". See *Chapter 3, Register Description* for more information of this Interrupt Register.

IRQ\* will be valid whenever the external interrupt occurs.

Figure 2-4 shows the timing for an interrupt acknowledge cycle.

Figure 2-4. Timing for Interrupt Acknowledge Cycle

## **Program Example**

The following program example demonstrates how to access the registers on the HP E2259A. The example uses the VXIplug&play register reads and writes.

The example programs were developed with the ANSI C language using the HP VISA extensions. The programs were written and tested in Microsoft<sup>®</sup> Visual C++ but should compile under any standard ANSI C compiler.

To run the programs you must have the HP SICL Library, the HP VISA extensions, and an HP 82340 or 82341 HP-IB module installed and properly configured in your PC. An HP E1406 Command Module is required for the first program. The HP E2259A must be installed in an HP E2251A Carrier for access to the A16 VXI registers.

The example programs reset the HP E2259A Breadboard M-Module. It then:

- Reads the ID, Device Type, Status, and A24 Memory Offset Registers.

- Writes a value to the I/O Register to output data on BC0 BC15,

- Writes a value to the WP0 Register to output data on BC0 BC15,

- Reads a value from the I/O Register to input data on TR0 TR15.

- Reads a value from the RP0 Register to input data on TR0 TR15.

#include <visa.h>

#include <stdio.h>

#include <stdlib.h>

ViSession viRM,m\_mod; int main() {

unsigned short id\_reg,dt\_reg ; unsigned short stat\_reg, a24\_offset ; short value; /\* ID & Device Type Registers \*/ /\* Status & A24 Offset Reg \*/ /\* register variable \*/

ViStatus errStatus;

/\*Status from each VISA call\*/

```

/* Open the default resource manager */

errStatus = viOpenDefaultRM ( &viRM);

if (VI_SUCCESS > errStatus){

printf("ERROR: viOpenDefaultRM() returned 0x%x\n",errStatus);

return errStatus;}

```

/\* Open the M-Module instrument session \*/

errStatus = viOpen(viRM,"GPIB-VXI0::8",VI\_NULL,VI\_NULL,&m\_mod);

if (VI\_SUCCESS > errStatus){

printf("ERROR: viOpen() returned 0x%x\n",errStatus);

return errStatus;}

/\* read and print the module's ID Register \*/

errStatus = viln16(m\_mod,VI\_A16\_SPACE,0x00,&id\_reg);

if (VI\_SUCCESS > errStatus){

printf("ERROR: viln16() returned 0x%x\n",errStatus);

return errStatus;}

printf("ID register = 0x%4X\n", id\_reg);

/\* read and print the module's Device Type Register \*/

errStatus = viln16(m\_mod,VI\_A16\_SPACE,0x02,&dt\_reg);

if (VI\_SUCCESS > errStatus){

printf("ERROR: viln16() returned 0x%x\n",errStatus);

return errStatus;}

printf("Device Type register = 0x%4X\n", dt\_reg);

/\* read and print the module's Status Register \*/

errStatus = viln16(m\_mod,VI\_A16\_SPACE,0x04,&stat\_reg);

if (VI\_SUCCESS > errStatus){

printf("ERROR: viln16() returned 0x%x\n",errStatus);

return errStatus;}

printf("Status register = 0x%hx\n", stat\_reg);

/\* read and print the module's A24 Offset Register \*/

errStatus = viln16(m\_mod,VI\_A16\_SPACE,0x06,&a24\_offset);

if (VI\_SUCCESS > errStatus){

printf("ERROR: viOpen() returned 0x%x\n",errStatus);

return errStatus;}

printf("A24 Offset register value = 0x%hx\n", a24\_offset);

/\* Write a value of AA to I/O Register, Addr 0x14 \*/

errStatus = viOut16(m\_mod,VI\_A24\_SPACE,0x14,0xAA);

if (VI\_SUCCESS > errStatus){

printf("ERROR: viOut16() returned 0x%x\n",errStatus);

return errStatus;}

/\* Write a value of FF to WP0 Register, Addr 0x20 \*/

errStatus = viOut16(m\_mod,VI\_A24\_SPACE,0x20,0xFF);

if (VI\_SUCCESS > errStatus){

printf("ERROR: viOut16() returned 0x%x\n",errStatus);

return errStatus;}

/\* Read the value from I/O Register, Addr 0x14 \*/

errStatus = viln16(m\_mod,VI\_A24\_SPACE,0x14,&value);

if (VI\_SUCCESS > errStatus){

printf("ERROR: viOut16() returned 0x%x\n",errStatus);

return errStatus;}

printf("0x14 register value = 0x%hx\n", value);

/\* Read the value from WPO Register, Addr 0x20 \*/

errStatus = viln16(m\_mod,VI\_A24\_SPACE,0x20,&value);

if (VI\_SUCCESS > errStatus){

printf("ERROR: viOut16() returned 0x%x\n",errStatus);

return errStatus;}

printf("0x20 register value = 0x%hx\n", value);

/\* Close the M-Module Instrument Session \*/

errStatus = viClose (m\_mod);

if (VI\_SUCCESS > errStatus) {

printf("ERROR: viClose() returned 0x%x\n",errStatus);

return 0;}

/\* Close the Resource Manager Session \*/

errStatus = viClose (viRM);

if (VI\_SUCCESS > errStatus) {

printf("ERROR: viClose() returned 0x%x\n",errStatus);

return 0;}

return VI\_SUCCESS;

}

# **Resetting the Module**

There are two ways to reset the module and your own external circuitry. The CRST\* signal line is available on J102 which is available to reset your circuitry (active low).

- **Hardware Reset** Whenever you apply power to the system, the HP E2259A breadboard module will also be reset. This pulses the CRST\* line low.

- **Software Reset** You can also write a "1" to bit 0 of the Control Register (address  $04_h$  in A16 memory, refer to Chapter 3 for details). This will reset the M-Module and pulse the CRST\* line. You must write a "0" to bit 0 of the Control Register after the reset is finished.

## **Using the Power Supplies**

Each power supply available for use by external circuits is protected by a positive-temperature-coefficient thermistor. When maximum current through the thermistor is reached, it heats up, and its resistance increases significantly thereby limiting the current; the thermistor acts like a resettable fuse. Table 2-4 lists the power supplies, thermistor protection reference designator (silkscreened on PC board), and the maximum current.

| Table 2-4. HP E2259A Power Supply Protection | Table | 2-4. H | P E2259A | Power | Supply | Protection |

|----------------------------------------------|-------|--------|----------|-------|--------|------------|

|----------------------------------------------|-------|--------|----------|-------|--------|------------|

|               | Thermistor Ref.<br>Designator | Maximum Current | Connector | Application                                                                                        |

|---------------|-------------------------------|-----------------|-----------|----------------------------------------------------------------------------------------------------|

| +5VDC Supply  | F201                          | 1000mA          | J102      | Main power source for all systems.<br>Used for supplying power to logic device.                    |

| +12VDC Supply | F200                          | 200mA           | Near J102 | General purpose power for switching power convertors, analog devices and disc drives.              |

| -12VDC Supply | F202                          | 200mA           | Near J102 | General purpose power for analog devices<br>and disc drives. Not recommended for power convertors. |

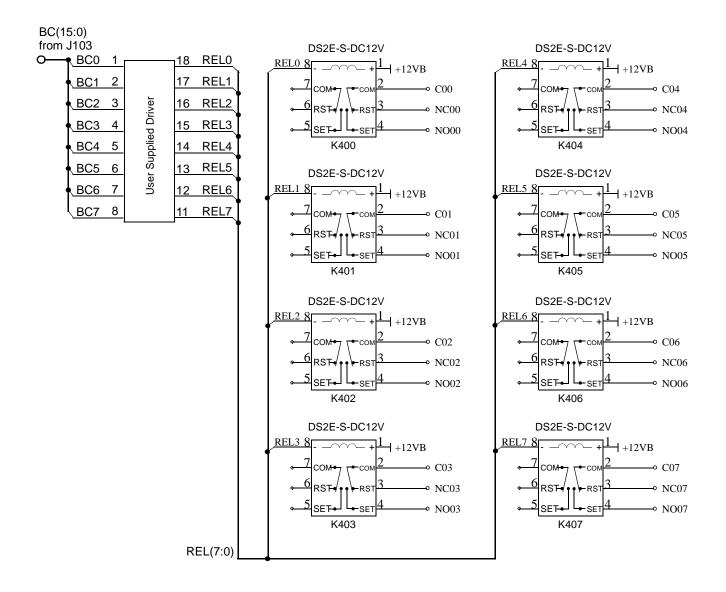

# **Application Example**

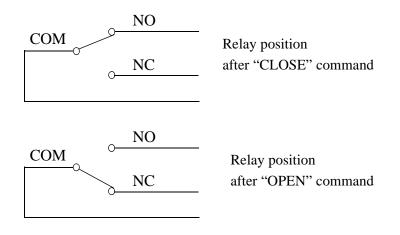

This section contains a simplified example application using the breadboard module as an 8-channel Form-C Relay module. See Figure 2-6. You must supply the relay driver IC, flyback protection, etc. These have been omitted from the drawing for simplification.

**Relay Selection** The I/O Register is used as the interface. To open one specific relay, you need to WRITE a "0" to the bit of the I/O Register which corresponds to that relay. To close a channel, you need to write a "1" to the corresponding I/O Register bit.

#### Figure 2-5. Write a "1" or "0" to the Register Bit to Close/Open the Relay

The status of all relays must be specified simultaneously. To change just one relay, it is necessary to change the corresponding bit and send the entire pattern again.

The 16-bit I/O Register of HP E2259A is used to control and readback 8 Form-C Relays.

# **About This Chapter**

This chapter contains register addressing information; it also provides the register description of HP E2259A Double-Wide Breadboard M-Module. Chapter contents include:

- Register Addressing in the VXI Environment ..... Page 31

- Register Descriptions ..... Page 37

# **Register Addressing in the VXIbus Environment**

| Logical Address           | Each module in a VXIbus (VXI) system, whether VXI or M-Module, must<br>have a unique logical address. The HP E2251 Carrier provides a logical<br>address for each installed M-Module. Refer to the HP E2251 Installation and<br>Getting Started Guide for details (if you are using a different carrier, refer to<br>that carrier's documentation for register-based addressing information).                                                                                                                                                                          |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

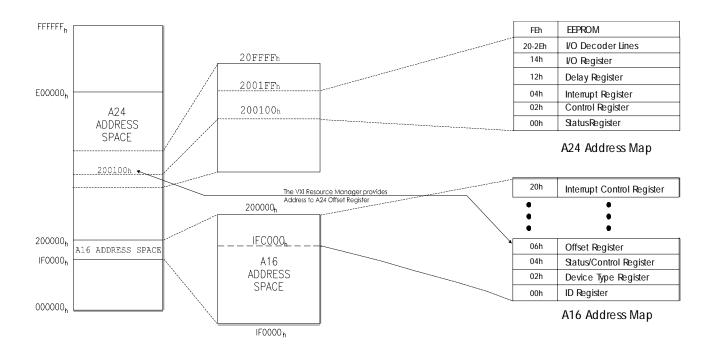

| A16/A24 Memory<br>Mapping | The VXI Specification allows for only 64 bytes of address space in A16 memory. However, the M-Module Specification defines 256 bytes of address space. To resolve this conflict, the HP E2251 Carrier provides two memory segments for each installed M-Module. The first is in the VXI A16 memory space and contains the standard VXI registers. The second memory segment is in the VXI A24 memory space and contains all other M-Module registers (these registers are described starting on Page 41). Figure 3-1 shows the A16/A24 mapping for a typical M-Module. |

| Note                      | The M-Module's ID word (from the ID EEPROM) is mapped into the VXI Manufacturer ID Register at address $00_h$ and the M-Module's VXI Device Type word is mapped into the VXI Device Type Register at address $02_h$                                                                                                                                                                                                                                                                                                                                                    |

**Note** Most of the descriptions in this chapter assume the HP E2259A is installed in an HP E2251A Carrier. The Carrier provides access to the VXI registers.

\* Base Address = 1FC000<sub>16</sub> + (Logical Address \* 64)<sub>16</sub> or = 2,080,768<sub>10</sub> + (Logical Address \* 64)<sub>10</sub>

A16 Register Address = Base Address + Register Offset

For M-Modules, the Register Address is Computed as: Base Address = Value in Offset Register Register Address = Base Address Combines the Register Offset (A24 address space)

For Example, in above case, the I/O Register Address is: I/O Register Address = 200100<sub>16</sub> + 14<sub>16</sub> = 200114<sub>16</sub> or = 2.097.408<sub>10</sub> + 20<sub>10</sub> = 2.907.428<sub>10</sub>

Figure 3-1. A16/A24 Memory Mapping

## Determining a Module's A16 Base Address

To access a register in A16 memory, you must specify a hexadecimal or decimal register address. This address consists of a base address plus a register offset. The A16 base address depends on whether or not you are using an HP E1406 Command Module.

A16 Address Space Inside the Command Module When using an HP E1406 Command Module, the base address is computed as:

$1FC000_{h} + (LADDR_{h} \cdot 40_{h})$ or (decimal)  $2,080,768 + (LADDR \cdot 64)$

Where:

$1FC000_h$  (2,080,768) is the A16 starting address LADDR is the module's logical address

$40_{h}$  (64) is the number of address bytes allocated per module

For example, if the M-Module has a logical address of  $78_h$  (120) the A16 base address becomes:

$\begin{aligned} 1\text{FC000}_{\text{h}} + (78_{\text{h}} \cdot 40_{\text{h}}) &= 1\text{FC000}_{\text{h}} + 1\text{E00}_{\text{h}} = 1\text{FDE00}_{\text{h}} \\ or \quad (\text{decimal}) \\ 2,080,768 + (120 \cdot 64) &= 2,080,768 + 7680 = 2,088,448 \end{aligned}$

#### A16 Address Space Outside the Command Module

When an HP E1406 Command Module is <u>not</u> part of your system, the base address is computed as:

$C000_{h} + (LADDR_{h} \cdot 40_{h})$ or (decimal)  $49,152 + (LADDR \cdot 64)$

#### Where:

$C000_h$  (49,152) is the A16 starting address LADDR is the module's logical address  $40_h$  (64) is the number of address bytes allocated per module

For example, if the M-Module has a logical address of  $78_h$  (120) the A16 base address becomes:

$C000_{h} + (78_{h} \cdot 40_{h}) = C000_{h} + 1E00_{h} = DE00_{h}$ or (decimal)  $49,152 + (120 \cdot 64) = 49,152 + 7680 = 56,832$

## Addressing A16 Registers

As shown in Figure 3-1, VXI registers for an M-Module are mapped into A16 address space by the HP E2251 Carrier. To access one of these registers, add the A16 base address to the register offset. For example, an M-Module's VXI Status/Control Register has an offset of  $04_h$ . To access this register (assuming the system <u>does not</u> have an HP E1406 Command Module), use the register address:

$1FDE00_{h} + 04_{h} = 1FDE04_{h}$ or (decimal) 2,088,488 + 4 = 2,088,452

## Addressing A24 Registers

As shown in Figure 3-1, most of the registers for an M-Module are mapped into A24 address space. To access one of these registers:

- 1. Obtain the A24 base address by reading the VXI Offset Register  $(06_h)$  in A16 memory.

- 2. Add the A24 base address to the register offset (see Table 3-2).

For example, if the A24 base address is  $200100_{h}$ , to access the Output Register (10<sub>h</sub>):

$200100_{\rm h} + 10_{\rm h} = 200110_{\rm h}$

*or* (decimal) 2,097,408 + 16 = 2,097,424

# **Program Example**

The following sample program demonstrates how to write to and read from registers on the HP E2259A. The program was developed with the ANSI C language using the HP VISA extensions. The program was written and tested in Microsoft Visual C++ but should compile under any standard ANSI C compiler.

To run the program you must have the HP SICL Library, the HP VISA extensions, and an HP 82340 or 82341 HP-IB module installed and properly configured in your PC. An HP E1406 Command Module provides direct access to the VXI backplane. The HP E2259A must be installed in an HP E2251A Carrier for access to the A16 VXI Registers.

#include <visa.h>

#include <stdio.h>

#include <stdlib.h>

ViSession viRM,m\_mod

int main() { ViStatus errStatus:

/\*Status from each VISA call\*/ session\*/

/\* Open the default resource manager \*/

errStatus = viOpenDefaultRM (&viRM);

if(VI\_SUCCESS > errStatus){

printf("ERROR: viOpenDefaultRM() returned 0x%x\n",errStatus);

return errStatus;}

/\* Open the M-Module instrument session \*/

errStatus = viOpen(viRM,INSTR\_ADDR, VI\_NULL,VI\_NULL,&m\_mod);

if(VI\_SUCCESS > errStatus){

printf("ERROR: viOpen() returned 0x%x\n",errStatus);

return errStatus;}

/\* read and print the module's ID Register \*/

errStatus = viln16(m\_mod,VI\_A16\_SPACE,0x00,&id\_reg);

if (VI\_SUCCESS > errStatus){

printf("ERROR: viln16() returned 0x%x\n",errStatus);

return errStatus;}

printf("ID register = 0x%hx\n", id\_reg);

/\* read and print the module's Device Type Register \*/

errStatus = viln16(m\_mod,VI\_A16\_SPACE,0x02,&dt\_reg);

if (VI\_SUCCESS > errStatus){

printf("ERROR: viln16() returned 0x%x\n",errStatus);

return errStatus;}

printf("Device Type register = 0x%hx\n", dt reg);

/\* read and print the module's Status Register \*/

errStatus = viln16(m\_mod,VI\_A16\_SPACE,0x04,&stat\_reg);

if (VI\_SUCCESS > errStatus){

printf("ERROR: viln16() returned 0x%x\n",errStatus);

return errStatus;}

printf("Status register = 0x%hx\n", stat\_reg);

/\* read and print the module's A24 Offset Register \*/ errStatus = viln16(m\_mod,VI\_A16\_SPACE,0x06,&a24\_offset); if(VI SUCCESS > errStatus){ printf("ERROR: viOpen() returned 0x%x\n",errStatus); return errStatus;} printf("A24 Offset register value = 0x%hx\n", a24\_offset); /\* set the BUSY Delay Timer to 15mS (see Busy Timer) \*/ errStatus = viOut16 (m mod,VI A24 SPACE,0x12,0x1D6); if (VI SUCCESS > errStatus){ printf("ERROR: viOut16() returned 0x%x\n",errStatus); return errStatus;} /\* Output a Value of 5 on BCn Data Lines \*/ errStatus = viOut16 (m\_mod,VI\_A24\_SPACE,0x14,0x05); if (VI SUCCESS > errStatus){ printf("ERROR: viOut16() returned 0x%x\n",errStatus); return errStatus;} /\* Close the M-Module Instrument Session \*/ err\_status = viClose (m\_mod); if (VI SUCCESS > errStatus) { printf("ERROR: viClose() returned 0x%x\n",errStatus); return 0:} /\* Close the Resource Manager Session \*/ err status = viClose (viRM); if (VI\_SUCCESS > errStatus) { printf("ERROR: viClose() returned 0x%x\n",errStatus); return 0;} return VI\_SUCCESS;

}

## **Register Descriptions**